82LS180-F,N • 82LS181-F,N

#### DESCRIPTION

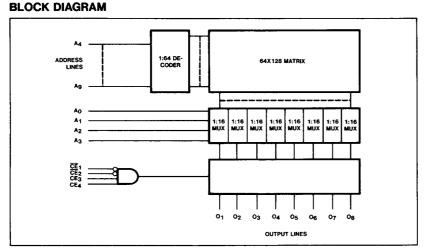

The 82LS180 and 82LS181 are field programmable, which means that custom patterns are immediately available by following the fusing procedure given in this data sheet. The standard 82LS180 and 82LS181 are supplied with all outputs at logical low. Outputs are programmed to a logic high level at any specified address by fusing a Ni-Cr link matrix.

These devices include on-chip decoding and 4 chip enable inputs for ease of memory expansion. They feature either open collector or 3-state outputs for optimization of word expansion in bused organizations.

The 82LS180 and 82LS181 are available in both the commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N82LS180/181, F or N, and for the military temperature range (-55°C to +125°C) specify S82LS180/181, F.

### **FEATURES**

- · Address access time: N82LS180/181: 175ns max S82LS180/181: 225ns max

- Power dissipation: 37μW/bit typ

- Input loading:

- N82LS180/181: -100μA max S82LS180/181: -150µA max

- On-chip address decoding

- Output options:

- 82LS180: Open collector 82LS181: 3-state

- No separate fusing pins

- . Unprogrammed outputs are low level

- Fully TTL compatible

### **APPLICATIONS**

- Prototyping/volume production

- Sequential controllers

- Microprogramming

- · Hardwired algorithms

- Control store Random logic

- Code conversion

# **ABSOLUTE MAXIMUM RATINGS**

| +7<br>+5.5<br>+5.5 | Vdc<br>Vdc<br>Vdc |

|--------------------|-------------------|

| +5.5<br>+5.5       | Vdc               |

| +5.5               |                   |

|                    | Vdc               |

|                    |                   |

| 1                  |                   |

| +5.5               |                   |

|                    | °C                |

|                    | 1                 |

| 0 to +75           |                   |

| -55 to +125        |                   |

| -65 to +150        |                   |

|                    | -55 to +125       |

128

# signetics

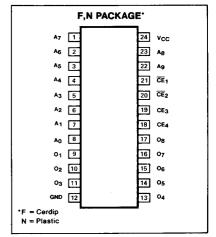

### PIN CONFIGURATION

DC ELECTRICAL CHARACTERISTICS N82LS180/181: 0°C $\leq$  T<sub>A</sub>  $\leq$  +75°C, 4.75V  $\leq$  V<sub>CC</sub>  $\leq$  5.25V S82LS180/181:  $-55^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  +125°C, 4.5V  $\leq$  V<sub>CC</sub>  $\leq$  5.5V

|                         |                                                             |                                                                                                                                                                                                         |                                                                               |     | N82LS180/181     |                 |     | S82LS180/181     |                |                |

|-------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|------------------|-----------------|-----|------------------|----------------|----------------|

|                         | PARAMETER                                                   | TEST COND                                                                                                                                                                                               | ITIONS1                                                                       | Min | Typ <sup>2</sup> | Max             | Min | Typ <sup>2</sup> | Max            | UNIT           |

| VIL<br>VIH<br>VIC       | Input voltage<br>Low<br>High<br>Clamp                       | I <sub>IN</sub> = -18                                                                                                                                                                                   | i <sub>IN</sub> = -18mA                                                       |     | -0.8             | .85<br>-1.2     | 2.0 | -0.8             | .80<br>-1.2    | · V            |

| V <sub>OL</sub><br>VOH  | Output voltage<br>Low<br>High (82LS181)                     | $\begin{array}{c} \text{I}_{\text{OUT}} = 4.\\ \hline \text{CE}_1 = \text{low, I}_{\text{OUT}}\\ \text{CE}_2 = \text{k}\\ \text{CE}_2 = \text{high, } \hline{\text{CE}}\\ \text{high stoi} \end{array}$ | $\Gamma = -1 \text{mA},$ $E_4 = \text{high},$                                 | 2.4 |                  | 0.45            | 2.4 |                  | 0.5            | V              |

| հը<br>ՌН                | Input current<br>Low<br>High                                | V <sub>IN</sub> = 0.4<br>V <sub>IN</sub> = 5.                                                                                                                                                           |                                                                               |     |                  | -100<br>40      |     |                  | -150<br>50     | μΑ             |

| OLK<br>O(OFF)           | Output current<br>Leakage (82LS180)<br>Hi-Z state (82LS181) | $\overline{CE}_1 = \overline{CE}_2 = HIGH$ $CE_3 = CE_4 = LOW$                                                                                                                                          | V <sub>OUT</sub> = 5.5V<br>V <sub>OUT</sub> = 0.5V<br>V <sub>OUT</sub> = 5.5V |     |                  | 40<br>-40<br>40 |     |                  | 60<br>60<br>60 | μΑ<br>μΑ<br>μΑ |

| los                     | Short circuit (82LS181)                                     | $\overline{CE}_1 = \overline{CE}_2 = LOW,$<br>$CE_2 = CE_3 = HIGH$                                                                                                                                      | V                                                                             | -10 |                  | -70             | -10 |                  | -85            | mA             |

| lcc                     | V <sub>CC</sub> supply current                              |                                                                                                                                                                                                         |                                                                               |     | 60               | 80              |     | 60               | 85             | mA             |

| C <sub>IN</sub><br>COUT | Capacitance<br>Input<br>Output                              | V <sub>IN</sub> = 2.                                                                                                                                                                                    | V <sub>CC</sub> = 5.0V<br>V <sub>IN</sub> = 2.0V<br>V <sub>OUT</sub> = 2.0V   |     | 5<br>8           |                 |     | 5<br>8           |                | pF             |

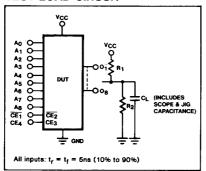

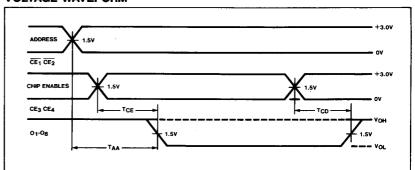

# AC ELECTRICAL CHARACTERISTICS $R_1 = 1k\Omega$ , $R_2 = 2k\Omega$ , $C_L = 30pF$

N82LS180/181: 0°C  $\leq$  T<sub>A</sub>  $\leq$  +75°C, 4.75V  $\leq$  V<sub>CC</sub>  $\leq$  5.25V  $882LS180/181: -55°C \le T_A \le +125°C, 4.5V \le V_{CC} \le 5.5V$

|                                    |              |                  | FROM                   | N82LS180/181 |                  |           | S82LS180/181 |                  |           |      |

|------------------------------------|--------------|------------------|------------------------|--------------|------------------|-----------|--------------|------------------|-----------|------|

|                                    | PARAMETER    | то               |                        | Min          | Typ <sup>2</sup> | Max       | Min          | Typ <sup>2</sup> | Max       | UNIT |

| T <sub>AA</sub><br>T <sub>CE</sub> | Access time  | Output<br>Output | Address<br>Chip enable |              | 100<br>35        | 175<br>60 |              | 100<br>35        | 225<br>80 | ns   |

| ™CD                                | Disable time | Output           | Chip disable           |              | 35               | 50        |              | 35               | 70        | ns   |

#### NOTES

- 1. Positive current is defined as into the terminal referenced.

- 2. Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = +25$ °C.

82LS180-F,N • 82LS181-F,N

## **TEST LOAD CIRCUIT**

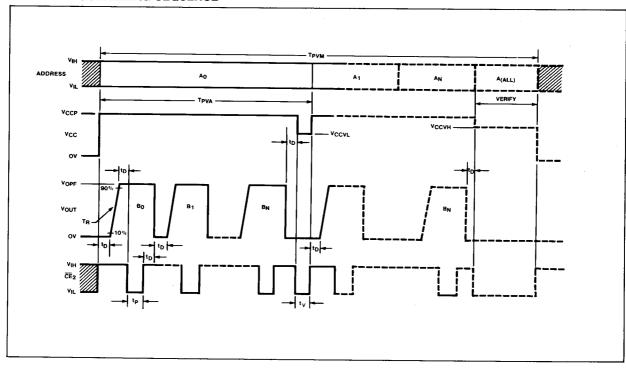

# **VOLTAGE WAVEFORM**

# PROGRAMMING SYSTEM SPECIFICATIONS<sup>4</sup> (Testing of these limits may cause programming of device.) T<sub>A</sub> = +25°C

| PARAMETER          |                                                 | TEST CONDITIONS                             |      | UNIT |      |            |

|--------------------|-------------------------------------------------|---------------------------------------------|------|------|------|------------|

|                    |                                                 |                                             | Min  | Тур  | Max  | Jidi       |

|                    | Power supply voltage                            |                                             |      |      |      | v          |

| V <sub>CCP</sub>   | To program <sup>1</sup>                         | ICCP = 425±75mA, Transient or steady state  | 8.5  |      | 9.0  |            |

|                    | Verify limit                                    |                                             |      |      |      | v          |

| V <sub>СС</sub> ∨н | Upper                                           |                                             | 5.3  |      | 5.7  |            |

| VCCVL              | Lower                                           |                                             | 4.3  |      | 4.7  |            |

| Vs                 | Verify threshold <sup>2</sup>                   |                                             | 1.4  |      | 1.6  | v          |

| ICCP               | Programming supply current                      | $V_{CCP} = +8.75 \pm .25V$                  | 350  |      | 500  | m.A        |

|                    | Input voltage                                   |                                             |      |      |      | V          |

| V <sub>IH</sub>    | High                                            |                                             | 2.4  |      | 5.5  |            |

| V <sub>IL</sub>    | Low                                             |                                             | 0    |      | 0.8  |            |

|                    | Input current                                   |                                             |      |      |      | μΑ         |

| ۱н                 | High                                            | V <sub>IH</sub> = +5.5V                     |      |      | 50   |            |

| l <sub>IL</sub>    | Low                                             | $V_{IL} = +0.4V$                            |      |      | -500 |            |

| VOPF               | Forced output voltage <sup>3</sup><br>(program) | IOPF = 200 ±20mA, Transient or steady state | 16.0 |      | 18.0 | V          |

| IOPF               | Forced output current (program)                 | $V_{OPF} = +17 \pm 1V$                      | 180  |      | 220  | m <i>A</i> |

| TR                 | Output pulse rise time                          |                                             | 10   |      | 1    | μs         |

| tp                 | CE programming pulse width                      |                                             | 100  |      | 125  | μ <b>s</b> |

| tD                 | Pulse sequence delay                            |                                             | 5    | 1    |      | μ8         |

| tv                 | CE verify pulse width                           |                                             | 1    |      |      | μ8         |

| TPVA               | Address program verify cycle                    |                                             |      |      | 1    | ms         |

| TPVM               | Memory program verify time (continuous)         |                                             |      |      | 20   | se         |

| FL                 | Fusing attempts per link                        |                                             |      |      | 1 1  | сус        |

#### NOTES

- I. Bypass  $V_{\hbox{\scriptsize CC}}$  to GND with a 0.01 $\mu\hbox{\scriptsize F}$  capacitor to reduce voltage spikes.

- V<sub>S</sub> is the sensing threshold of the PROM output voltage for a programmed bit. It

normally constitutes the reference voltage applied to a comparator circuit to verify a

successful fusing attempt.

- 3. This voltage should be maintained within specified limits during the entire fusing cycle.

- For a transient current of 150mA, limit voltage spikes to a maximum slew rate of  $2V/\mu s$ , and  $10\mu s$  maximum recovery.

- 4. These are specifications which a Programming System must satisfy in order to be qualified by Signetics. They contain new limits for minimizing total device programming time, which supersede, but do not obsolete the performance requirements of previously manufactured programming equipment.

130

# Signetics

82LS180-F,N • 82LS181-F,N

## PROGRAMMING PROCEDURE

- 1. Terminate all device outputs with a  $10k\Omega$  resistor to  $V_{CC}$ . Apply  $\overline{CE}_1$  = Low,  $\overline{CE}_2$  = High,  $CE_3$  = High,  $CE_4$  = High.

- Select the Address to be programmed, and raise V<sub>CC</sub> to V<sub>CCP</sub>.

- After to delay, apply V<sub>OPF</sub> to the output to be programmed. Program one output at the time.

- After t<sub>D</sub> delay, pulse the CE<sub>2</sub> input to logic low for a time t<sub>p</sub>.

- After to delay, remove Vopp from the programmed output.

- 6. Repeat steps 3 through 5 to program other bits at the same address.

- To verify programming of all bits at the same address after tp delay, lower V<sub>CC</sub> to V<sub>CCVL</sub> and apply a logic low level to

- the  $\overline{\text{CE}}_2$  input. All programmed outputs should remain in the logic high state.

- After to delay, repeat steps 2 through 7 to program and verify all other address locations.

- After tp delay, raise V<sub>CC</sub> to V<sub>CCVH</sub> and verify all memory locations by applying a logic low level to CE<sub>2</sub>, and cycling through all device addresses.

## TYPICAL PROGRAMMING SEQUENCE