# **NEC Microcomputers, Inc.**

NEC μPD4164-1 μPD4164-2 μ PD4164-3

# 65,536 x 1 BIT DYNAMIC RANDOM ACCESS MEMORY

### DESCRIPTION

The NEC  $\mu$ PD4164 is a 65,536 words by 1 bit Dynamic N-Channel MOS RAM designed to operate from a single +5V power supply. The negative-voltage substrate bias is internally generated — its operation is both automatic and transparent.

The  $\mu$ PD4164 utilizes a double-poly-layer N-channel silicon gate process which provides high storage cell density, high performance and high reliability.

The µPD4164 uses a single transistor dynamic storage cell and advanced dynamic circuitry throughout, including the 512 sense amplifiers, which assures that power dissipation is minimized. Refresh characteristics have been chosen to maximize yield (low cost to user) while maintaining compatibility between Dynamic RAM generations.

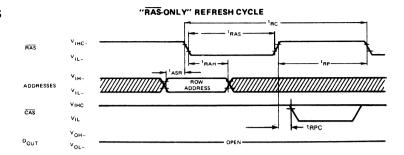

The  $\mu$ PD4164 three-state output is controlled by  $\overline{CAS}$ , independent of  $\overline{RAS}$ . After a valid read or read-modify-write cycle, data is held on the output by holding  $\overline{CAS}$  low. The data out pin is returned to the high impedance state by returning  $\overline{CAS}$  to a high state. The  $\mu$ PD4164 hidden refresh feature allows  $\overline{CAS}$  to be held low to maintain output data while  $\overline{RAS}$  is used to execute  $\overline{RAS}$  only refresh cycles.

Refreshing is accomplished by performing  $\overline{RAS}$  only refresh cycles, hidden refresh cycles, or normal read or write cycles on the 128 address combinations of A0 through A6 during a 2 ms period.

Multiplexed address inputs permit the  $\mu$ PD4164 to be packaged in the standard 16 pin dual-in-line package. The 16 pin package provides the highest system bit densities and is compatible with widely available automated handling equipment.

### **FEATURES**

- High Memory Density

- Multiplexed Address Inputs

- Single +5V Supply

- On Chip Substrate Bias Generator

- Access Time: μPD4164-1 250 ns

$\mu$ PD4164-2 - 200 ns  $\mu$ PD4164-3 - 150 ns

- Read, Write Cycle Time:  $\mu$ PD4164-1 410 ns  $\mu$ PD4164-2 335 ns

- $\mu$ PD4164-2 335 ns  $\mu$ PD4164-3 270 ns

- Low Power Dissipation: 250 mW (Active); 28 mW (Standby)

- Non-Latched Output is Three-State, TTL Compatible

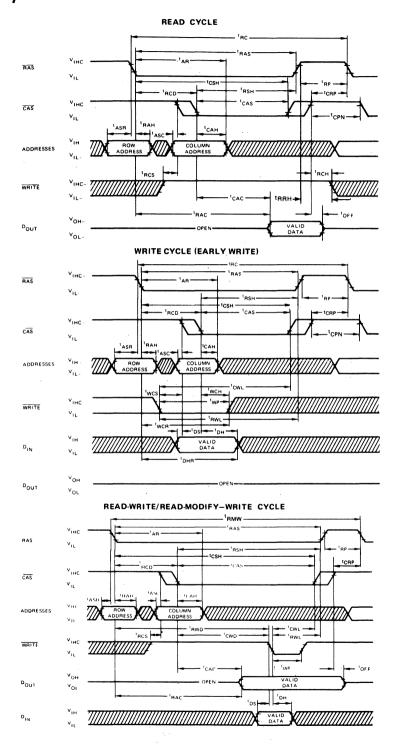

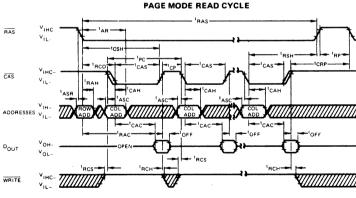

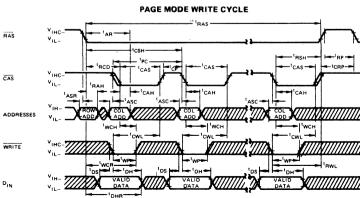

- Read, Write, Read-Write; Read-Modify-Write, RAS Only Refresh, and Page Mode Capability

- All Inputs TTL Compatible, and Low Input Capacitance

- 128 Refresh Cycles (An-An Pins for Refresh Address)

- CAS Controlled Output Allows Hidden Refresh

- Available in Both Ceramic and Plastic 16 Pin Packages

### PIN CONFIGURATION

|                                | PIN NAMES             |

|--------------------------------|-----------------------|

| A <sub>0</sub> -A <sub>7</sub> | Address Inputs        |

| RAS                            | Row Address Strobe    |

| CAS                            | Column Address Strobe |

| WE                             | Write Enable          |

| DIN                            | . Data Input          |

| DOUT                           | Data Output           |

| vcc                            | Power Supply (+5V)    |

| V <sub>SS</sub>                | Ground                |

| NC                             | No Connection         |

# μPD4164

| Operating Temperature                                | ABSOLUTE MAXIMUM |

|------------------------------------------------------|------------------|

| Storage Temperature (Ceramic Package)55°C to +150°C  | RATINGS*         |

| (Plastic Package)55°C to +125°C                      |                  |

| Supply Voltages On Any Pin Except VCC1 to +7 Volts ① |                  |

| Supply Voltage V <sub>CC</sub>                       |                  |

| Short Circuit Output Current                         |                  |

| Power Dissipation                                    |                  |

| Note: ① Relative to Vss                              |                  |

Note: (1) Relative to VSS

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

\*Ta = 25°C

$T_a = 0^\circ \text{ to } 70^\circ \text{C}$  (1);  $V_{CC} = +5V \pm 10\%$ ;  $V_{SS} = 0V$

|                                                                                                                   |      |                   |      | LIMITS |     |      | TEST                       |

|-------------------------------------------------------------------------------------------------------------------|------|-------------------|------|--------|-----|------|----------------------------|

| PARAMETER                                                                                                         | S١   | MBOL              | MIN  | TYP    | MAX | UNIT | CONDITIONS                 |

| Supply Voltage                                                                                                    |      | Vcc               | 4.5  | 5.0    | 5.5 | >    |                            |

|                                                                                                                   |      | V <sub>SS</sub>   | 0    | 0      | 0   | V    |                            |

| High Level Input Voltage.<br>(RAS, CAS, WE)                                                                       | ,    | VIHC              | 2.4  |        | 5.5 | ٧    | All Voltages<br>Referenced |

| High Level Input Voltage,<br>All Inputs Except RAS,<br>CAS, WE                                                    |      | VIH               | 2.4  |        | 5.5 | ٧    | to V <sub>SS</sub>         |

| Low Level Input Voltage,<br>All Inputs                                                                            |      | VIL               | -2.0 |        | 0.8 | >    |                            |

| Operating Current Average Power Supply                                                                            |      | μPD4164-1         |      |        | 45  |      | ,                          |

| Operating Current                                                                                                 | Icc1 | μPD4164-2         |      |        | 50  | mA   | 2                          |

| RAS, CAS Cycling;<br>tRC = tRC (Min.)                                                                             |      | μPD4164-3         |      |        | 60  |      |                            |

| Standby Current Power Supply Standby Current (RAS = VIHC, DOUT = Hi-Impedance)                                    |      | I <sub>CC2</sub>  |      |        | 5.0 | mA   |                            |

| Refresh Current<br>Average Power Supply                                                                           |      | μPD4164-1         |      |        | 35  |      |                            |

| Current,<br>Refresh Mode;                                                                                         | 1cc3 | μPD4164-2         |      |        | 40  | mA   | 2                          |

| RAS Cycling, CAS = V <sub>IHC</sub> ,<br>t <sub>RC</sub> = t <sub>RC</sub> (Min.)                                 |      | μPD4164-3         |      |        | 45  |      |                            |

| Page Mode Current<br>Average Power Supply                                                                         |      | μPD4164-1         |      |        | 35  |      |                            |

| Current,<br>Page Mode Operation                                                                                   | ICC4 | μPD4164-2         |      |        | 40  | mA   | 2                          |

| RAS = V <sub>IL</sub> ; CAS Cycling tpC = tpC (Min.)                                                              |      | μPD4164-3         |      |        | 45  |      |                            |

| Input Leakage Current<br>Any Input<br>V <sub>IN</sub> = 0 to +5.5 Volts,<br>All Other Pins Not<br>Under Test = 0V |      | li(L)             | -10  |        | 10  | μΑ   |                            |

| Output Leakage Current DOUT is Disabled, VOUT = 0 to +5.5 Volts                                                   |      | <sup>1</sup> O(L) | -10  |        | 10  | μΑ   |                            |

| Output Levels High Level Output                                                                                   |      | Vон               | 2.4  |        | Vcc | v    |                            |

| Voltage (IOUT = 5 mA) Low Level Output Voltage (IOUT = 4.2 mA)                                                    |      | VoL               | 0    |        | 0.4 | ٧    |                            |

Notes: ① T<sub>a</sub> is specified here for operation at frequencies to t<sub>RC</sub> ≥ t<sub>RC</sub> (min). Operation at higher cycle rates with reduced ambient temperatures and high power dissipation is permissible, however, provided AC operating parameters are met.

② I<sub>CC1</sub>, I<sub>CC3</sub> and I<sub>CC4</sub> depend on output loading and cycle rates. Specified rates are

obtained with the output open.

DC CHARACTERISTICS

## AC CHARACTERISTICS

$T_a = 0^{\circ} \text{ to } +70^{\circ} \text{ C} \bigcirc; V_{CC} = +5V \pm 10\%; V_{SS} = 0V \bigcirc \bigcirc$

|                                                  |                  | LIMITS |        |      |                                                  |     |              |      |            |  |

|--------------------------------------------------|------------------|--------|--------|------|--------------------------------------------------|-----|--------------|------|------------|--|

|                                                  | 1                | μPD    | 4164-1 | μPD4 | 164-2                                            | μPD | 4164-3       | ]    | TEST       |  |

| PARAMETER                                        | SYMBOL           | MIN    | MAX    | MIN  | MAX                                              | MIN | MAX          | UNIT | CONDITIONS |  |

| Random Read or Write<br>Cycle Time               | tRC              | 410    |        | 335  |                                                  | 270 |              | ns   | <b>⑤</b>   |  |

| Read Write Cycle Time                            | tRWC             | 465    |        | 335  | 1                                                | 270 |              | ns   | 6          |  |

| Page Mode Cycle Time                             | tPC              | 275    |        | 225  |                                                  | 170 |              | ns   |            |  |

| Access Time from RAS                             | tRAC             |        | 250    |      | 200                                              |     | 150          | ns   | 6 8        |  |

| Access Time from CAS                             | tCAC             |        | 165    |      | 135                                              |     | 100          | ns   | <b>⑦</b> ® |  |

| Output Buffer Turn-Off<br>Delay                  | tOFF             | 0      | 60     | 0    | 50                                               | 0.  | 40           | ns   | 9          |  |

| Transition Time (Rise and Fall)                  | tΤ               | 3      | 50     | 3    | 50                                               | 3   | 50           | ns   | 4          |  |

| RAS Precharge Time                               | tRP              | 150    |        | 120  |                                                  | 100 |              | ns   |            |  |

| RAS Pulse Width                                  | tRAS             | 250    | 10,000 | 200  | 10,000                                           | 150 | 10,000       | ns   |            |  |

| RAS Hold Time                                    | tRSH             | 165    |        | 135  |                                                  | 100 |              | ns   |            |  |

| CAS Pulse Width                                  | tCAS             | 165    | 10,000 | 135  | 10,000                                           | 100 | 10,000       | ns   |            |  |

| CAS Hold Time                                    | tCSH             | 250    |        | 200  |                                                  | 150 |              | ns   |            |  |

| RAS to CAS Delay Time                            | tRCD             | 35     | 85     | 30   | 65                                               | 25  | 50           | ns   | 0          |  |

| CAS to RAS Precharge Time                        | tCRP             | 0      |        | 0    |                                                  | 0   | ļ            | ns   |            |  |

| CAS Precharge Time                               | tCPN             | 35     |        | 30   |                                                  | 25  |              | ns   |            |  |

| CAS Precharge Time (For<br>Page Mode Cycle Only) | tCP              | 100    |        | 80   |                                                  | 60  |              | ns   |            |  |

| RAS Precharge CAS Hold<br>Time                   | TRPC             | 0      |        | 0    |                                                  | 0   |              | ns   |            |  |

| Row Address Set-Up Time                          | †ASR             | 0      |        | 0    |                                                  | 0   |              | ns   |            |  |

| Row Address Hold Time                            | tRAH             | 25     |        | 20   | <del>                                     </del> | 15  | <del> </del> | ns   |            |  |

| Column Address Set-Up<br>Time                    | tASC             | 0      |        | 0    |                                                  | 0   |              | ns   |            |  |

| Column Address Hold Time                         | †CAH             | 75     |        | 55   |                                                  | 45  |              | ns   |            |  |

| Column Address Hold Time<br>Referenced to RAS    | <sup>t</sup> AR  | 160    |        | 120  |                                                  | 95  |              | ns   |            |  |

| Read Command Set-Up<br>Time                      | tRCS             | 0      |        | 0    |                                                  | 0   |              | ns   |            |  |

| Read Command Hold Time<br>Referenced to RAS      | terh             | 30     |        | 25   |                                                  | 20  |              | ns   | G)         |  |

| Read Command Hold Time                           | tRCH-            | 0      |        | 0    |                                                  | 0   |              | ns   | (3         |  |

| Write Command Hold Time                          | tWCH             | 75     |        | 55   |                                                  | 45  |              | ns   |            |  |

| Write Command Hold Time<br>Referenced to RAS     | ·WCR             | 160    |        | 120  |                                                  | 95  |              | ns   |            |  |

| Write Command Pulse Width                        | twp              | 75     |        | 55   |                                                  | 45  |              | ns   |            |  |

| Write Command to RAS<br>Lead Time                | <sup>†</sup> RWL | 100    |        | 55   |                                                  | 45  |              | ns   |            |  |

| Write Command to CAS<br>Lead Time                | tCWL             | 100    |        | 55   |                                                  | 45  |              | ns   |            |  |

| Data-In Set-Up Time                              | tps              | 0      |        | 0    |                                                  | 0   |              | ns   | 0          |  |

| Data-In Hold Time                                | †DH              | 75     |        | 55   |                                                  | 45  |              | ns   | 0          |  |

| Data-In Hold Time<br>Referenced to RAS           | <sup>t</sup> DHR | 160    |        | 120  |                                                  | 95  |              | ns   |            |  |

| Refresh Period                                   | †REF             |        | 2      |      | 2                                                |     | 2            | ms   |            |  |

| WRITE Command Set-Up<br>Time                     | twcs             | -20    |        | -20  |                                                  | -20 |              | ns   | Ø          |  |

| CAS to WRITE Delay                               | tCWD             | 115    |        | 80   |                                                  | 60  |              | ns   | 0          |  |

| RAS to WRITE Delay                               | tRWD             | 200    |        | 145  | T                                                | 110 | I            | ns   | 0          |  |

- Notes: ① T<sub>8</sub> is specified here for operation at frequencies to t<sub>RC</sub> > t<sub>RC</sub> (min). Operation at higher cycle rates with reduced ambient temperatures and higher power dissipation is permissible, however, provided AC operating parameters are met.

- ② An initial pause of 100  $\mu s$  is required after power-up followed by any 8  $\overline{RAS}$  cycles before proper device operation is

- 3 AC measurements assume t<sub>T</sub> = 5 ns.

- V<sub>IHC</sub> (min) or V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IHC</sub> or V<sub>IH</sub> and V<sub>IL</sub>.

- ⑤ The specifications for t<sub>RC</sub> (min) and t<sub>RWC</sub> (min) are used only to indicate cycle times at which proper operation over the full temperature range (0° C < T<sub>a</sub> < 70° C) is assured.</p>

- Assumes that tRCS < tRCD (max). If tRCS is greater than the maximum recommended value shown in this table, tRAC will increase by the amount that tRCD exceeds the values shown.

</p>

- Assumes that tRCD > tRCD (max).

- (8) Measured with a load equivalent to 2 TTL loads and 100 pF.

- toff (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- Operation within the tRCD (max) limit ensures that tRAC (max) can be met, tRCD (max) is specified as a reference point only, if tRCD is greater than the specified tRCD (max) limit, then access time is controlled exclusively by tCAC.

These parameters are referenced to CAS leading edge in early write cycles and to WRITE leading edge in delayed write or read-modify-write cycles.

- ② Either tRRH or tRCH must be satisfied for a read cycle.

# TIMING WAVEFORMS (CONT.)

# HIDDEN REFRESH CYCLE MEMORY CYCLE - IPP - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAAA - IAAA - IAAA - IAAA - IAAA - IAAAA - IAAAA - IAAAA - IAAA - IAAAA - IA

$T_a = 0^{\circ} \text{ to } +70^{\circ}\text{C}; V_{CC} = +5\text{V} \pm 10\%; V_{SS} = 0\text{V}$

| PARAMETER                                                               | SYMBOL          |     | LIMITS | 3   | UNIT | TEST       |

|-------------------------------------------------------------------------|-----------------|-----|--------|-----|------|------------|

| PANAMETEN                                                               | STMBUL          | MIN | TYP    | MAX | UNIT | CONDITIONS |

| Input Capacitance<br>(A <sub>0</sub> -A <sub>7</sub> ), D <sub>IN</sub> | C <sub>I1</sub> |     | 5      | 6   | рF   |            |

| Input Capacitance<br>RAS, CAS, WRITE                                    | C <sub>12</sub> | ĸ.  | ; .    | 10  | pF   |            |

| Output Capacitance<br>(DOUT)                                            | C <sub>0</sub>  |     |        | 7   | pF   |            |

# CAPACITANCE

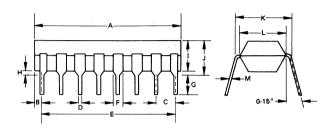

PACKAGE OUTLINES  $\mu PD4164C$

Plastic

| ITEM | MILLIMETERS         | INCHES    |

|------|---------------------|-----------|

| Α    | 19.4 MAX.           | 0.76 MAX. |

| В    | 0.81                | 0.03      |

| С    | 2.54                | 0.10      |

| D    | 0.5                 | 0.02      |

| E    | 17.78               | 0.70      |

| F    | 1.3                 | 0.051     |

| G    | 2.54 MIN.           | 0.10 MIN. |

| н    | 0.5 MIN.            | 0.02 MIN. |

| ı    | 4.05 MAX.           | 0.16 MAX. |

| J    | 4.55 MAX.           | 0.18 MAX. |

| K    | 7.62                | 0.30      |

| L.   | 6.4                 | 0.25      |

| м    | 0.25 +0.10<br>-0.05 | 0.01      |

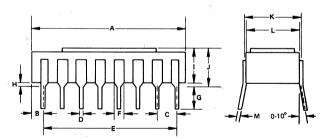

μPD4164D

Ceramic

| ITEM | MILLIMETERS | INCHES     |

|------|-------------|------------|

| Α    | 20.5 MAX.   | 0.81 MAX   |

| В    | 1.36        | 0.05       |

| С    | 2.54        | 0.10       |

| D    | 0.5         | 0.02       |

| E    | 17.78       | 0.70       |

| F    | 1.3         | 0.051      |

| G    | 3.5 MIN.    | 0.14 MIN.  |

| н    | 0.5 MIN.    | 0.02 MIN.  |

| 1    | 4.6 MAX.    | 0.18 MAX   |

| J    | 5.1 MAX.    | . 0.20 MAX |

| K    | 7.6         | 0.30       |

| L    | 7.3         | 0.29       |

| м    | 0.27        | 0.01       |